Memopak : bad RAM chips ?

Re: Memopak : bad RAM chips ?

That's nice - please show us you nuclear reactor you control with this fancy board.

Re: Memopak : bad RAM chips ?

It is actually part of the Tele-porting device project

32K SRAM WRX compatible, 32Bit IO-Port, ROM Ghost, ZX-Printer.

Re: Memopak : bad RAM chips ?

So here i am again, pity all the soldering was done already when i found out about the HiRes thingy, I did notice a pull-up resistor referring to HiRes on Mark's Mod explanation, but since i see now there is actually something on the RD relating to !RFSH, i figure i probably don't need to worry about that (yet) as far as i can make up out of the doc mentioning modifying Ram-packs is that an AND-gate can be constructed out of 2 Germanium diodes and a pull-up resistor on the !RD of the ram chip, now i'm wondering whether that would be before or after the !MREQ-!RD gate in other words, does !MREQ go low during the refresh cycle ? it is also a pity i don't have any AND-gates left open, i do have an OR, 2 NOR's and a couple of NOT gates, but i don't want to slow the signal down to much, the SRAM takes 70ns and the LS gates take about 8ns each and as far as i understood the whole thing has to be done in about 110ns i read that somewhere i think, don't remember where though i could actually reorganize the use of the gates in such a way that i use a NOR gate where i am using an AND gate at the moment... hmmm i wish i would have known this earlier. Anyway if anybody knows if the !MREQ also goes low during the refresh cycle this would be very helpful.

32K SRAM WRX compatible, 32Bit IO-Port, ROM Ghost, ZX-Printer.

Re: Memopak : bad RAM chips ?

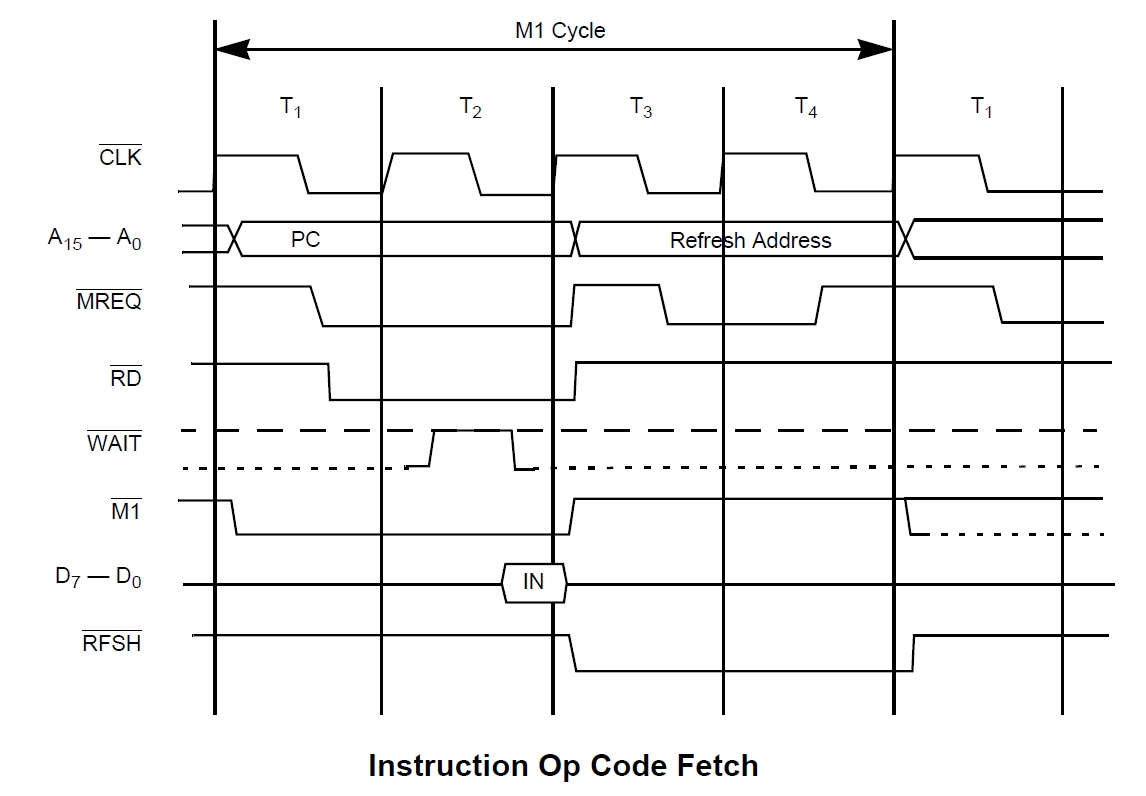

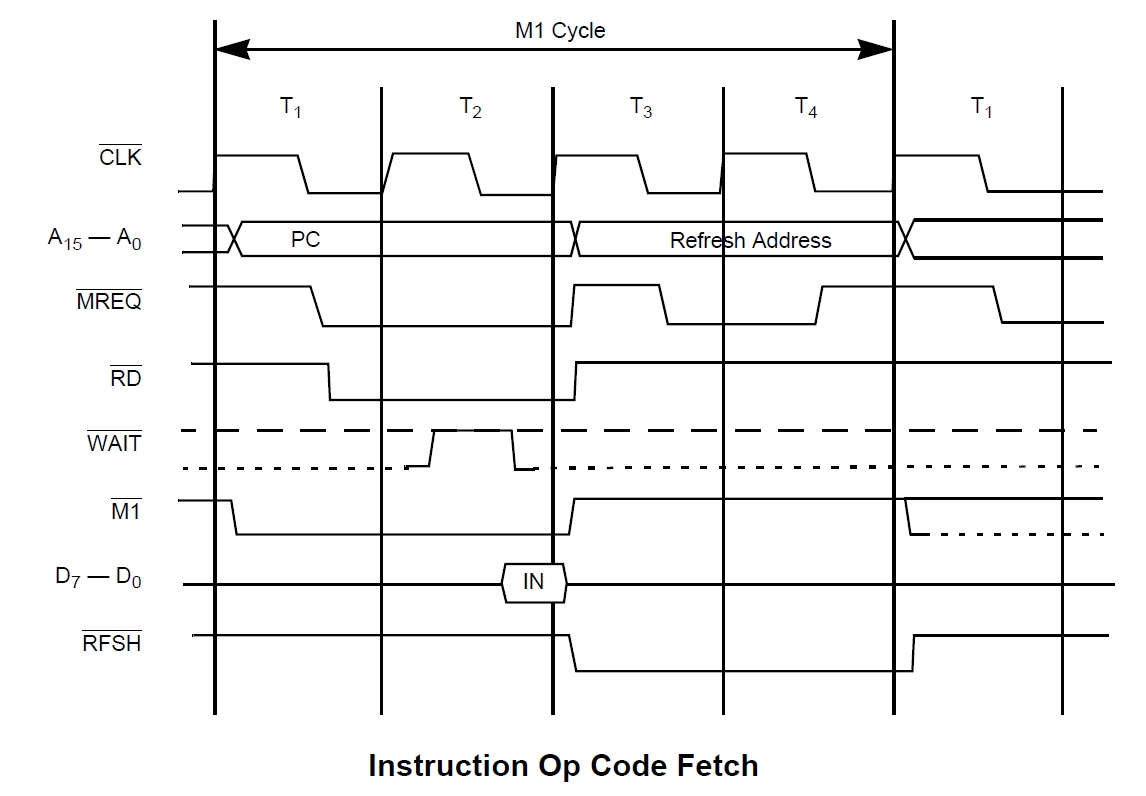

Here is your ressource (timing - M1 - instruction fetch):

http://www.farnell.com/datasheets/91822.pdf

MREQ goes down but only for one clock cycle which would give time of about 300ns.

But the video shift register is loaded with the rising edge of (the next) M1 - so MREQ has been off long time.

Usually RD and RFSH can be ORed with two schottky diodes and a pullup resistor - so you don't need an extra gate.

See here:

http://sinclairzxworld.com/viewtopic.php?f=6&t=61#p383

Instead of the gate you may use a 10k pullup between /RD of RAM and Vcc and then connect this pin via two diodes to /RD and /RFSH of CPU. So this works as /RD of RAM is pulled down either when a normal /RD is or when a /RFSH cycle is present. The cathode of the two diodes go to /RD and /RFSH of CPU.

http://www.farnell.com/datasheets/91822.pdf

MREQ goes down but only for one clock cycle which would give time of about 300ns.

But the video shift register is loaded with the rising edge of (the next) M1 - so MREQ has been off long time.

Usually RD and RFSH can be ORed with two schottky diodes and a pullup resistor - so you don't need an extra gate.

See here:

http://sinclairzxworld.com/viewtopic.php?f=6&t=61#p383

Instead of the gate you may use a 10k pullup between /RD of RAM and Vcc and then connect this pin via two diodes to /RD and /RFSH of CPU. So this works as /RD of RAM is pulled down either when a normal /RD is or when a /RFSH cycle is present. The cathode of the two diodes go to /RD and /RFSH of CPU.

Re: Memopak : bad RAM chips ?

Hold on ! Ok, we have 300ns that's heaps, a lot more then I thought anyway, but eh OR-ed ? either one of them has to go low for a RD request doesn't it ? if i use an OR gate they'd both have to go low before it goes low, or not ? it's the inversion that makes this stuff so tricky, atm i have !RD on the RAM via an OR of !RD and !MREQ. does !RD go low during a screen refresh iow when !RFSH goes low ?! I didn't think so, but does it ? if !MREQ goes low during a !RFSH then i could (and probably should put an AND gate on !RD and !RFSH that is sort of what this is suggesting but RD || RFSH = a request then !RD && !RFSH = a !request anyway you're saying that !MREQ does go low during a refresh cycle, right ?

32K SRAM WRX compatible, 32Bit IO-Port, ROM Ghost, ZX-Printer.

- 1024MAK

- Posts: 5119

- Joined: Mon Sep 26, 2011 10:56 am

- Location: Looking forward to summer in Somerset, UK...

Re: Memopak : bad RAM chips ?

I think there is some confusion

The "wired-OR" is a type of OR gate, as in with both, or either input at the active logic level (in this case, the active level is a logic zero/low), the output will be active (zero/low).

And yes, if using an actual logic gate, you need to use a AND gate rather than a OR gate.

If you have active low functions, and want OR, use AND. If you want AND, use OR gates etc...

Don't forget, you can make a OR gate from NAND gates, or make a AND gate from NOR gates.

Mark

The "wired-OR" is a type of OR gate, as in with both, or either input at the active logic level (in this case, the active level is a logic zero/low), the output will be active (zero/low).

And yes, if using an actual logic gate, you need to use a AND gate rather than a OR gate.

If you have active low functions, and want OR, use AND. If you want AND, use OR gates etc...

Don't forget, you can make a OR gate from NAND gates, or make a AND gate from NOR gates.

Code: Select all

/RFSH /RD OR NOR AND NAND

0 0 0 1 0 1

0 1 1 0 0 1

1 0 1 0 0 1

1 1 1 0 1 0

^ ^

| |

Mark

ZX81 Variations

ZX81 Chip Pin-outs

ZX81 Video Transistor Buffer Amp

Standby alert

Standby alert

There are four lights!

Step up to red alert. Sir, are you absolutely sure? It does mean changing the bulb

Looking forward to summer later in the year.

ZX81 Chip Pin-outs

ZX81 Video Transistor Buffer Amp

There are four lights!

Step up to red alert. Sir, are you absolutely sure? It does mean changing the bulb

Looking forward to summer later in the year.

Re: Memopak : bad RAM chips ?

Thank you Mark, there was some confusion, at least i had it clear it clear in my head but Pokemon's answer confused me a little but now it is clear, also where to put the active-low OR-gate, or an actual AND-gate, cause i think that's what i'll put. The cycle-map makes it all clear. this is not going to be so high on my list but but now i do know what to do.

32K SRAM WRX compatible, 32Bit IO-Port, ROM Ghost, ZX-Printer.

Re: Memopak : bad RAM chips ?

Sorry - mostly people talk from wired OR but in fact it is a wired AND.

https://de.wikipedia.org/wiki/Wired-AND

But be sure to use /RFSH & /RD and not /MREQ & /RD. The video shift register is sure loaded at the end of M1 or better beginning of next M1 cycle. There is a little overhang of RFSH and the first clock cycle which is used in this context to read the char data from RAM.

https://de.wikipedia.org/wiki/Wired-AND

But be sure to use /RFSH & /RD and not /MREQ & /RD. The video shift register is sure loaded at the end of M1 or better beginning of next M1 cycle. There is a little overhang of RFSH and the first clock cycle which is used in this context to read the char data from RAM.

Re: Memopak : bad RAM chips ?

Well at the moment i've got it wired up

(!MERQ || !RD) -> RD(on Ram)

i'm using standard C++ logic notation just to make sure no confusion occurs.

Of course this works, but not for HiRes, so the plan was to change that to

(!RFSH && !RD) || !MERQ -> RD(on Ram)

I've never had HiRes working on my ZX81, and i tried Dr Beeps marble racer with just the 1K but that didn't work either, maybe i didn't get the proper version. i'm driffting of topic here, and as i said it's no a priority at the moment. Maybe i should start a new Topic about the HiRes later i can experiment a little once i've relocated / changed the address multiplexing of the IO port to free one AND gate up. focusing first on some software, and USR routines. i had some success with it as a teenager, but i had not assembler editor, played with that for the first time today, Wow that helps the whole thing about digging the ZX81 up was to get working what i didn't manage before. In the process i realized that one of my favorite toys was also responsible for me not learning to type with 10 fingers, so i've been fixing that as well.

the whole thing about digging the ZX81 up was to get working what i didn't manage before. In the process i realized that one of my favorite toys was also responsible for me not learning to type with 10 fingers, so i've been fixing that as well.

(!MERQ || !RD) -> RD(on Ram)

i'm using standard C++ logic notation just to make sure no confusion occurs.

Of course this works, but not for HiRes, so the plan was to change that to

(!RFSH && !RD) || !MERQ -> RD(on Ram)

I've never had HiRes working on my ZX81, and i tried Dr Beeps marble racer with just the 1K but that didn't work either, maybe i didn't get the proper version. i'm driffting of topic here, and as i said it's no a priority at the moment. Maybe i should start a new Topic about the HiRes later i can experiment a little once i've relocated / changed the address multiplexing of the IO port to free one AND gate up. focusing first on some software, and USR routines. i had some success with it as a teenager, but i had not assembler editor, played with that for the first time today, Wow that helps

32K SRAM WRX compatible, 32Bit IO-Port, ROM Ghost, ZX-Printer.

Re: Memopak : bad RAM chips ?

Now I got what you do with /MREQ.

That is okay - but most people do process /MREQ together with adress lines to a /CS (chip select) to avoid beeing used on IO adresses.

If /MREQ is used for/CS than you can just use an AND gate for /RD and /RFSH and give that output signal to /RD of RAM.

Just in case.

That is okay - but most people do process /MREQ together with adress lines to a /CS (chip select) to avoid beeing used on IO adresses.

If /MREQ is used for/CS than you can just use an AND gate for /RD and /RFSH and give that output signal to /RD of RAM.

Just in case.