This photograph was key:

The process for the Zilog Z80 is a Depletion-Type MOSFET Load architecture (nMOS transistors). It appears that the process is a 10um minimum gate length one. I would love to know if anyone knows any more specifics about the process used and especially if there are SPICE models for the devices.

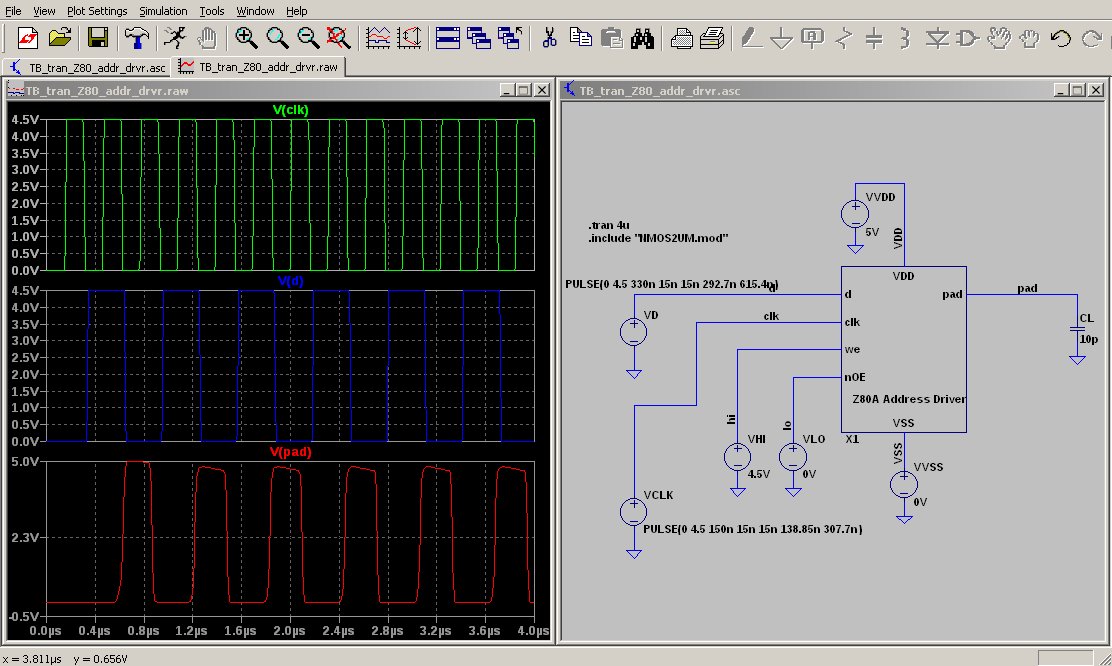

I was able to find a suitable substitute for the models and things seem to be functioning as expected:

LTspice files here: https://s3-us-west-2.amazonaws.com/file ... _spice.zip

So why go through this trouble? For one, I'm curious like most of us are. Secondly, I'm interested in what's happening at the A[8:0] A'[8:0] isolation resistors. I'm currently working on a Verilog model of the ZX81 and for a brief time during operation, there's a "drive fight" on the lower address lines when both the Z80 CPU is driving the line and the ULA is driving the line (during "refresh"). Often the logic values are complementary, hence the X in the digital simulation. Unfortunately Icarus doesn't support resistive primitives.